ISSN No. (Print) : 0975-8364 ISSN No. (Online) : 2249-3255

### A Reduced Switch Count Multilevel Module Multilevel Converter Topology

Karri V.V. Satyanarayana Assistant Professor, Department of Electrical Engineering, Nirma University, Gujarat, India.

(Corresponding author. Karri V.V. Satyanarayana) (Received 05 June 2019, Revised 06 August 2019, Accepted 15 September 2019) (Published by Research Trend, Website: www.researchtrend.net)

ABSTRACT: In this paper a new multilevel module multilevel converter (MLM-MLI) topology with reduced switch count is proposed. The proposed topology significantly reduces number of dc voltage sources, IGBT switches, switching power losses and gate driver circuitry. A comparative analysis of existing topology and proposed topology has been carried out for eleven level multilevel converter. The analytical analysis and optimization structure of proposed new MLM-MLI and its submultilevel converter is also presented. Operation and performance of proposed eleven level converter topology tested with dissimilar types of multicarrier pulse width modulation (MCPWM) techniques, precisely in-phase disposition (IPD), anti-phase opposition disposition (APOD), carrier overlap (CO) and variable frequency PWM techniques. The results have been confirmed in MATLAB/Simulink in mandate to outstanding the superlative MCPWM technique that gives lowest THD in converter output voltage.

**Keywords:** Controlling schemes, multilevel inverter, optimal structures, switching states, submultilevel converter and voltage level generation.

**Abbreviations:** MLM-MLI, multilevel module multilevel inverter; MCPWM, multicarrier pulse width modulation; IPD-LSPWM, in-phase disposition level shifted pulse width modulation; APOD-LSPM, anti-phase opposition disposition level shifted pulse width modulation; CO-PWM, carrier overlap pulse width modulation; VFPWM-variable frequency pulse width modulation; BBBC, bidirectional blocking-bidirectional conducting; UBBC, unidirectional blocking-bidirectional conducting; THD, total harmonic distortion; FFT, Fast Fourier Transform (FFT).

### I. INTRODUCTION

Now a days in Power electronics, DC to AC adaptation plays a significant role. Exclusively to extract energy from photovoltaic systems, wind energy and bio fuel cells [1, 2]. The basic concept of multilevel inverter is used to generate staircase wave form by connecting several dc sources in series through semiconductor switches. Thus, the multilevel inverter (MLI) structures were industrialized [3]. It is necessary to use different type of modulation techniques [4] to control output voltage of multilevel inverters and reduce the total harmonic distortion in output voltage of multilevel inverter.

Multilevel inverters are used to produce n number of output voltage levels with large number of switching components. The switching components increases switching losses in inverter and decrease the efficiency of inverter. It necessary to reduce usage of switching components in multilevel inverter. The suggested topology greatly reduces switching components, switching losses and gate driver circuitry compared to traditional capacitor clamped inverters and other conventional inverter topologies [5, 6].

The multilevel inverter slant for dc to ac adaptation suggested numerous Benefits such as [7]. Bidirectional multilevel inverter topology for symmetric and asymmetric structures is reported in [8]. The topologies of [11, 12] point out the drawbacks of cascaded H-Bridge multilevel inverter topology, because of it required large number of switch count and high voltage stress on the device. The improved version of H-Bridge based multilevel converter topology has been presented in [13]. The topology of [14] consist of cascaded connection of submultilevel units with reduced switch count. Optimal design structure of cascaded multilevel inverter and pulse width modulated inverters are reported in [15,16]. The topology in [17] completely reduced the switch count in cascaded multilevel inverters. It produce the numerous voltage levels in output voltage for symmetrical inverter and asymmetrical configurations. Multilevel inverter topology based on hybrid control techniques are presented in [18]. Optimization assessment of multilevel inverters and it analytical analysis is reported in [19]. Similarly, some other upgraded multilevel inverter topologies with reduced switch count have been proposed in [20-25].

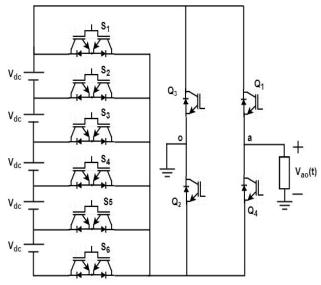

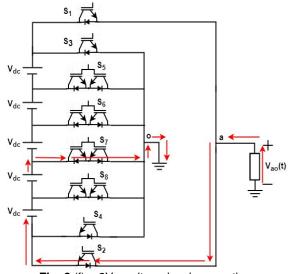

# II. GENERAL STRUCTURE OF EXISTING TOPOLOGY

The existing topology is also called as MLM-MLI topology [9,10]. This topology presents bidirectional blocking-bidirectional conducting (BBBC) switches for voltage level generation and unidirectional blocking-bidirectional conducting (UBBC) switches for polarity generation. The voltage stress on these switches are not dispersed consistently. Polarity generation switch endure the peak voltage produced by level generation switch. The single-phase multilevel module multilevel inverter (MLM-MLI) structure with contribution of five input dc voltage sources are shown in Fig. 1.

Fig. 1. Existing MLM-MLI Topology [9,10].

The valid operating states for voltage level generation and polarity generation are shown in table 1. This topology is facilitated symmetrical voltage source configuration. That means all five DC voltage sources have same magnitude (V<sub>DC</sub>). In each state of operation, three switches are conducted. Where one switch from voltage level generation and two switches from polarity generation. Thus in this topology, the polarity-generation switch blocked the maximum voltage stress of  $5V_{DC}$ each.

Table 1: Valid Switching States of Existing MLM-MLI Topology.

| State | Pole Voltage<br>[V <sub>ao</sub> (t)] | Active Switches                                  |

|-------|---------------------------------------|--------------------------------------------------|

| 1     | +V <sub>DC</sub>                      | $S_2$ , $Q_1$ , $Q_2$                            |

| 2     | +2V <sub>DC</sub>                     | S <sub>3</sub> , Q <sub>1</sub> , Q <sub>2</sub> |

| 3     | +3V <sub>DC</sub>                     | S <sub>4</sub> , Q <sub>1</sub> , Q <sub>2</sub> |

| 4     | +4V <sub>DC</sub>                     | $S_5$ , $Q_1$ , $Q_2$                            |

| 5     | +5V <sub>DC</sub>                     | S <sub>6</sub> , Q <sub>1</sub> , Q <sub>2</sub> |

| 6     | - V <sub>DC</sub>                     | S <sub>2</sub> , Q <sub>3</sub> , Q <sub>4</sub> |

| 7     | - 2V <sub>DC</sub>                    | S <sub>3</sub> , Q <sub>3</sub> , Q <sub>4</sub> |

| 8     | - 3V <sub>DC</sub>                    | S4 , Q3, Q4                                      |

| 9     | - 4V <sub>DC</sub>                    | S <sub>5</sub> , Q <sub>3</sub> , Q <sub>4</sub> |

| 10    | -5V <sub>DC</sub>                     | S <sub>6</sub> , Q <sub>3</sub> , Q <sub>4</sub> |

| 11    | 0                                     | $S_1$ , $Q_1$ , $Q_2$                            |

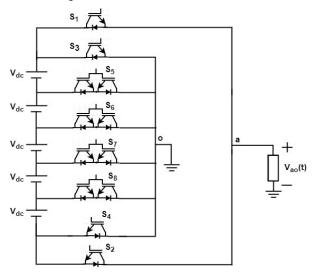

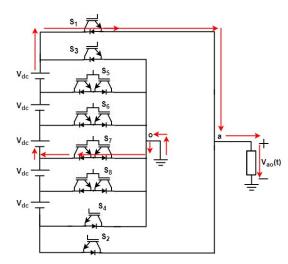

### **III. STRUCTURE OF PROPOSED TOPOLOGY**

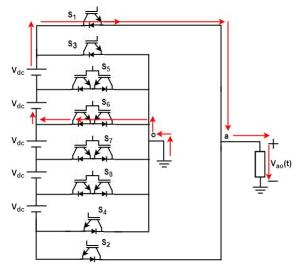

Proposed topology is known as a new multilevel module multilevel inverter topology with reduced switch count. Proposed MLM presents reduced switches compared to existing MLM. Existing MLM consist of four UBBC switches for polarity generation in the form of cascaded H bridge and remaining all switches are BBBC switches which are used to generate DC voltage level in converter output voltage. In proposed topology Cascaded H Bridge is completely eliminated and two switches are used for polarity generation. Where one switch is used for positive polarity generation and another switch is used for negative polarity generation. Proposed topology structure with reduced switch count is shown in Fig. 2.

In proposed topology, Switch S<sub>1</sub> is used for positive polarity generation and switch S<sub>2</sub> is used for negative polarity generation. Switches S<sub>3</sub>, S<sub>4</sub>, S<sub>5</sub>, S<sub>6</sub>, S<sub>7</sub>andS<sub>8</sub> are used for generating DC voltage level in converter output voltage waveform. Both positive and negative generation. Switches S<sub>1</sub> and S<sub>3</sub> are also used for generating zero voltage level. In proposed topology two switches are conducted in each state of switching but in existing MLM topology three switches are conducted in each state of switching but in each state of switching including polarity generation switches. So on state conducting switch count is less in proposed topology which leads to reduce the switching losses in multilevel inverter.

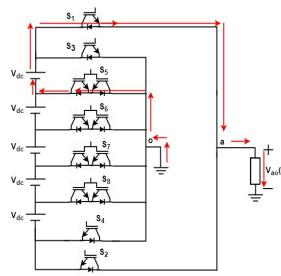

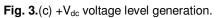

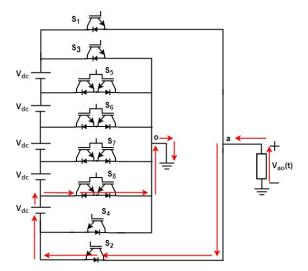

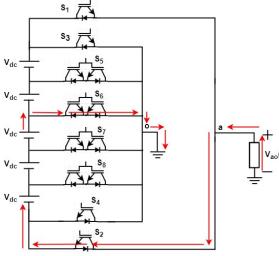

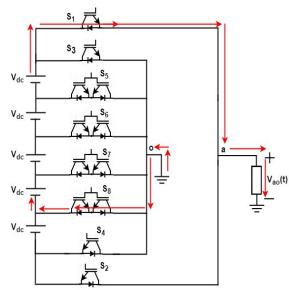

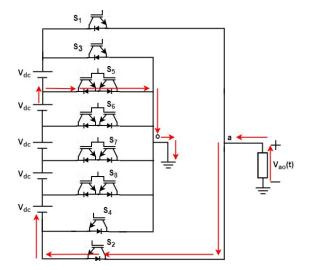

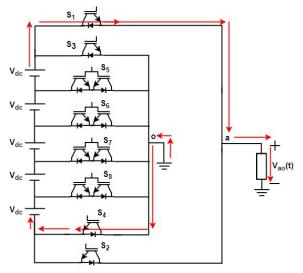

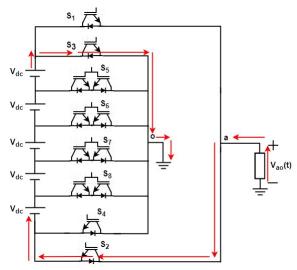

Proposed topology is configured for 11 level inverter and its switching states are shown in table. 2 and structure of switching states of suggested topology is shown in Fig. 3.

Fig. 2. Proposed MLM-MLI Topology.

| Table 2: Switching States of Proposed MLM-MLI |

|-----------------------------------------------|

| Topology.                                     |

| State | Pole Voltage<br>[V <sub>ao</sub> (t)] | Active Switches                 |

|-------|---------------------------------------|---------------------------------|

| 1     | +V <sub>DC</sub>                      | S <sub>1</sub> , S <sub>5</sub> |

| 2     | +2V <sub>DC</sub>                     | S <sub>1</sub> , S <sub>6</sub> |

| 3     | +3V <sub>DC</sub>                     | S <sub>1</sub> , S <sub>7</sub> |

| 4     | +4V <sub>DC</sub>                     | S <sub>1</sub> , S <sub>8</sub> |

| 5     | +5V <sub>DC</sub>                     | S <sub>1</sub> , S <sub>4</sub> |

| 6     | - V <sub>DC</sub>                     | S <sub>2</sub> , S <sub>8</sub> |

| 7     | - 2V <sub>DC</sub>                    | S <sub>2</sub> , S <sub>7</sub> |

| 8     | - 3V <sub>DC</sub>                    | S <sub>2</sub> , S <sub>6</sub> |

| 9     | -4V <sub>DC</sub>                     | S <sub>2</sub> , S <sub>5</sub> |

| 10    | -5V <sub>DC</sub>                     | S <sub>2</sub> , S <sub>3</sub> |

| 11    | 0                                     | S <sub>1</sub> , S <sub>3</sub> |

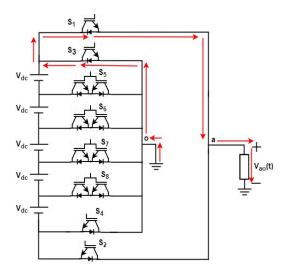

Fig. 3.(a) Zero voltage level generation.

Fig. 3.(b) Zero voltage level generation.

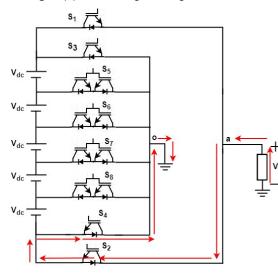

Fig. 3.(d)  $-V_{dc}$  voltage level generation.

Fig. 3.(e) +2 $V_{dc}$  voltage level generation.

**Fig. 3.**(f)  $-2V_{dc}$  voltage level generation.

Fig. 3.(g) +3 $V_{dc}$  voltage level generation.

Fig. 3.(h)  $-3V_{dc}$  voltage level generation.

Fig. 3.(i)  $+4V_{dc}$  voltage level generation.

Fig. 3.(j)  $-4V_{dc}$  voltage level generation.

Fig. 3.(k) +5 $V_{dc}$  voltage level generation.

**Fig. 3.**(I)  $-5V_{dc}$  voltage level generation.

| Parameter Comparison                                                | Existing MLM Topology | Modified MLM Topology |  |

|---------------------------------------------------------------------|-----------------------|-----------------------|--|

| Total Switches                                                      | 10                    |                       |  |

| Total Polarity Switches                                             | 04                    | 02                    |  |

| Bidirectional Blocking-Bidirectional Conducting (BBBC) Switches     | 06                    | 04                    |  |

| Unidirectional Blocking-Bidirectional<br>Conducting (UBBC) Switches | 04                    | 04                    |  |

| N Level (Total Number of Switches for Phase)                        | (N +1)/2+4            | (N - 3)/2+4           |  |

| N Level (Total Number of Switches for Three Phase)                  | 3(N +1)/2+12          | 3(N - 3)/2+12         |  |

Table 3: Differences between Two Topologies for 11 Level Inverter.

| Ctota | Switches States |                |    |                |    |   | V                |      |                  |    |                        |

|-------|-----------------|----------------|----|----------------|----|---|------------------|------|------------------|----|------------------------|

| State | S <sub>1</sub>  | S <sub>2</sub> | S₃ | S <sub>4</sub> | S₅ |   | S <sub>n-3</sub> | Sn-2 | S <sub>n-1</sub> | Sn | Vo                     |

| 1     | 1               | 1              | 0  | 0              | 0  |   | 0                | 0    | 0                | 0  | 0                      |

| 2     | 1               | 0              | 1  | 0              | 0  |   |                  | 0    | 0                | 0  | V <sub>1</sub>         |

| 3     | 0               | 0              | 0  | 0              | 0  |   |                  | 1    | 0                | 1  | $-V_1$                 |

| 4     | 1               | 0              | 0  | 1              | 0  |   |                  | 0    | 0                | 0  | $V_1+V_2$              |

| 5     | 0               | 0              | 0  | 0              | 0  |   | 1                | 0    | 0                | 1  | $-V_1 - V_2$           |

| :     | :               | :              | :  | :              |    | : |                  |      | :                | :  | :                      |

| :     | :               | :              | :  | :              |    | : |                  | :    | :                | :  | :                      |

| 2n    | 1               | 0              | 0  | 0              | 0  |   | 0                | 0    | 1                | 0  | $\sum_{i=1}^{n} V_i$   |

| 2n+1  | 0               | 1              | 0  | 0              | 0  |   | 0                | 0    | 0                | 1  | $-\sum_{i=1}^{n}V_{i}$ |

Table 4: Output voltage levels of submultilevel converter.

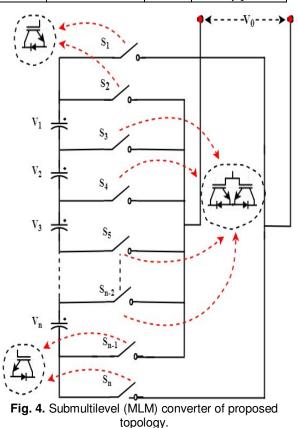

The comparison between existing topology and proposed topology for eleven level is shown in Table. 3. Proposed topology of submultilevel converter is shown in Fig. 4. This Submultilevel converter is also known as multilevel module (MLM). These submultilevel modules (MLMs) utilized for development of suggested topology. It consists of n number dc voltage sources and n number of IGBT switches, in which (n-4) switches are BBBC switches and 4switches are UBBC switches. It is found that only two switches are conducted to produce each voltage level of MLM. Generation of 2n+1 output voltage level of submultilevel converter is shown in table. 4. Here switches on state denoted by one (1) and switches off state denoted by zero (0).

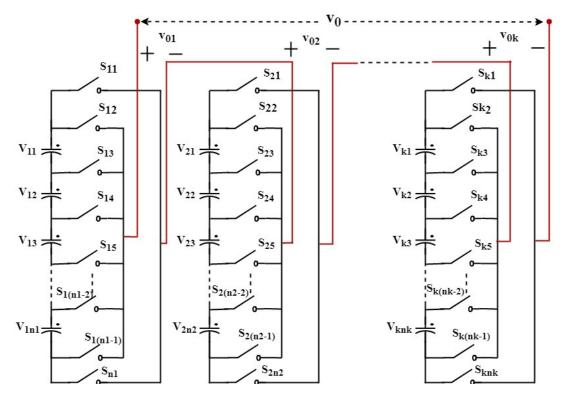

The suggested reduced switch count multilevel module multilevel converter topology for k number of multilevel modules are shown in Fig. 5. Here  $n_1, n_2, \ldots, n_k$  are n number of switches of first MLM to k<sup>th</sup> MLM respectively. Each submultilevel converter can be produced stepped output voltage waveform by different switching combination. Two switches are used to generate each output voltage level of submultilevel converter. Output voltage of proposed topology with reduced switch count will be obtained between  $-\sum_{i=1}^{k} \sum_{j=1}^{n_i} V_{ij}$  and  $+\sum_{i=1}^{k} \sum_{j=1}^{n_i} V_{ij}$  by proper selected values of dc voltage sources. Output voltage of suggested topology with submultilevel converter is shown in table. 5. In this topology capacitors can be replaced by renewable energy sources or fuel cells or dc batteries.

Fig. 5. Proposed multilevel converter topology.

Table 5: Switching states of proposed topology with reduced switch count.

| Switching State                | Output Voltage (V₀) |                      |   |                  |                               |                                                                       |

|--------------------------------|---------------------|----------------------|---|------------------|-------------------------------|-----------------------------------------------------------------------|

| 1                              | S <sub>11</sub>     | S <sub>12</sub>      |   | S <sub>k1</sub>  | S <sub>k2</sub>               | 0                                                                     |

| 2                              | S <sub>11</sub>     | S <sub>13</sub>      |   | S <sub>k1</sub>  | S <sub>k2</sub>               | V <sub>11</sub>                                                       |

| 3                              | S <sub>1n1</sub>    | S <sub>1(n1-3)</sub> |   | S <sub>k1</sub>  | S <sub>k2</sub>               | $-V_{11}$                                                             |

| :                              | :                   | ÷                    | : | :                | :                             |                                                                       |

| 2n1                            | S <sub>11</sub>     | S <sub>1(n1-1)</sub> |   | S <sub>k1</sub>  | S <sub>k2</sub>               | $\sum_{i=1}^{n} V_i$                                                  |

| $2n_1 + 1$                     | S <sub>12</sub>     | S <sub>1n1</sub>     |   | S <sub>k1</sub>  | S <sub>k2</sub>               | $-\sum_{i=1}^{n}V_{i}$                                                |

| :                              | :                   | :                    | : | :                | :                             | :                                                                     |

| $\prod_{i=1}^{k} (2n_i+1) - 3$ | S <sub>11</sub>     | S <sub>1(n1-1)</sub> |   | S <sub>knk</sub> | <i>S</i> <sub><i>k</i>2</sub> | $+\sum_{i=1}^{n_k} v_{ki} + \sum_{i=1}^{k-1} \sum_{i=1}^{n_i} V_{1i}$ |

| $\prod_{i=1}^{k} (2n_i+1) - 2$ | S <sub>12</sub>     | S <sub>1n1</sub>     |   | $S_{kn_k}$       | <i>S</i> <sub><i>k</i>2</sub> | $+\sum_{i=1}^{n_k} v_{ki} - \sum_{i=1}^{k-1} \sum_{i=1}^{n_i} V_{1i}$ |

| $\prod_{i=1}^{k} (2n_i+1) - 1$ | S <sub>11</sub>     | S <sub>1(n1-1)</sub> |   | $S_{kn_k}$       | <i>S</i> <sub><i>k</i>2</sub> | $-\sum_{i=1}^{n_k} v_{ki} + \sum_{i=1}^{k-1} \sum_{i=1}^{n_i} V_{1i}$ |

| $\prod_{i=1}^{k} (2n_i + 1)$   | S <sub>12</sub>     | S <sub>1n1</sub>     |   | $S_{kn_k}$       | S <sub>k2</sub>               | $-\sum_{i=1}^{n_k} v_{ki} - \sum_{i=1}^{k-1} \sum_{i=1}^{n_i} V_{1i}$ |

In this paper, asymmetrical multilevel module multilevel inverter with reduced switch count structure has been studied.

Considering  $V_{11}$  as the base voltage

$$V_{Base} = V_{11} = V_{dc} \tag{1}$$

Following algorithm is used to generate output voltage levels of suggested topology and different magnitudes of dc voltage sources are used to generate all output voltage levels. Per-unit system values are denoted, i.e.,

For mode 1

$V_{dc} = V_{11}$   $V_{1i} = V_{11} = V_{dc}, i = 2, 3, \dots, n_1$ For module 2 (2) (3)

(4)

$$\begin{split} V_{21} &= V_{11} + 2\sum_{i=1}^{n_1} V_{1i} = (2n_1 + 1) V_{dc} \\ V_{2i} &= V_{21} = (2n_1 + 1) V_{dc}, i = 2, 3, \dots, n_2 \end{split}$$

(5)

$$\begin{split} V_{31} &= V_{11} + 2\sum_{i=1}^{n_1}V_{1i} + 2\sum_{i=1}^{n_2}V_{2i} \\ V_{31} &= (2n_1+1)(2n_2+1)V_{dc} \end{split}$$

(6) (7)

International Journal on Emerging Technologies 10(3): 148-159(2019) Satyanarayana,

153

$V_{3i} = V_{31} = (2n_1 + 1)(2n_2 + 1)V_{dc}, i = 2, 3, \dots, n_3$  (8) In general, for m<sup>th</sup> module

$$V_{m1} = V_{11} + 2\sum_{\substack{i=1\\m-1}}^{m-1} \sum_{j=1}^{n-1} V_{ij}$$

(9)

$$V_{mi} = V_{m1} = \prod_{i=1}^{i=1} (2n_i + 1) V_{dc}, i = 2,3, \dots, n_m$$

(10)

Maximum value of the output voltage ( $V_{omax}$ ) of proposed topology is obtained by following equation:

$$V_{omax} = \sum_{i=1}^{\infty} \sum_{j=1}^{N} V_{ij} = \sum_{i=1}^{\infty} (n_i \times V_{i1})$$

(11)

Following equation is utilized to obtain number of output voltage levels:

$$N_{\text{level}} = \prod_{i=1}^{n} (2n_i + 1) \tag{12}$$

$N_{\text{level}} = (2n_1 + 1) \times (2n_2 + 1) \dots \dots \dots \times (2n_k + 1)$ (13)

Number of IGBTs in suggested topology can be obtained by following equation:

$$N_{IGBT} = 2(n_1 - 4) + 2(n_2 - 4) \dots \dots 2(n_k - 3) + 4k$$

(14)

#### **IV. OPTIMAL STRUCTURES**

A. Maximum Number of Voltage Levels with constant Number of IGBTS:

Considering (13) and(14) with all are equal in numbers for maximum number of voltage levels.

$$n_1 = n_2 = n_3 \cdots \cdots = n_k = n$$

(15)

Considering (14) and (15),

$$k = \frac{N_{IGBT}}{2(n-4)+4}$$

(16)

Maximum number of voltage levels will be obtained by considering the Eqns. (13) and (15),

$N_{\text{level}} = (2n+1)^k$  (17) Using (16) and (17),

$$N_{level} = \left[ (2n+1)^{1/(2(n-4)+4)} \right]^{N_{IGBT}}$$

(18)

Using (18), maximum number of voltage levels with constant number of IGBT switches can be obtained.

B. Maximum number of voltage levels with constant number of capacitors:

Considering suggested topology consists of a sequence of k number of MLMs and each one consists of  $n_i$ capacitors (i=1, 2, ..., k). Thus

$$N_{\text{capacitors}} = \sum_{i=1}^{n} n_i = n_1 + n_2 + \dots + n_k$$

(19)

Using (15), the number of capacitors can be written as follows:

$$N_{\text{capacitors}} = n \times k \tag{20}$$

Using (17), maximum number of voltage levels can be determined,

$$N_{\text{level}} = \left[ (2n+1)^{\frac{1}{n}} \right]^{N_{\text{capacitors}}}$$

(21)

Using (21), maximum number of voltage level with constant number of capacitors can be obtained.

C. Minimum number of IGBTS with constant number of voltage levels:

Considering (14) and (17), as follows:

$$N_{IGBT} = (2(n-4)+4)k$$

$$= ln(N_{\text{level}}) \times \frac{(2(n-4)+4)}{ln(2n+1)}$$

(22)

Using Eqn. (22), minimum Number of IGBTs with constant number of voltage levels can be obtained.

D. Minimum number of gate driver circuits with constant number of voltage levels:

The switches in each MLM of proposed topology assumed to be n, then total numbers of gate drive circuits ( $N_{driver}$ ) can be obtained, as follows:

$$N_{\rm driver} = ln(N_{\rm level}) \times \frac{(n)}{ln(2n+1)}$$

(23)

Using (23), for constant  $N_{\text{level}}$  minimum number of gate driver circuits can obtained.

## V. INVERTER OUTPUT VOLTAGE CONTROLLING SCHEMES

To normalize the inverter output voltage and plummeting the harmonic gratified in inverter output voltage, it must select the most suitable PWM method. In proposed MLM-MLI topology multi carrier sinusoidal PWM (SPWM) technique is functional to the switching devices, in which fundamental frequency of sinusoidal wave modulated with high frequency of triangular carrier wave(s). The generating DC level in inverter output Voltage is based on multi carrier PWM technique. Frequency and amplitude of the multiple carrier signals are diverse constructed on the PWM method. Unique modulation index is continued in all the approaches of multi carrier PWM for assessment. Amplitude of modulation index is the ratio of peak magnitude of reference sinusoidal wave to peak amplitude of high rate of recurrence carrier wave. Rate of recurrence modulation index is distinct as the ratio of carrier wave frequency to reference sinusoidal wave frequency. Notation of Amplitude modulation index and rate of recurrence modulation index are set by Eqn. (24) and (25) correspondingly.

$$M_A = \frac{A_m}{A_c} \tag{24}$$

$$M_F = \frac{F_C}{F_m} \tag{25}$$

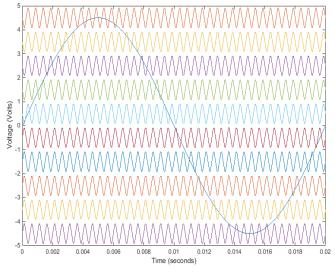

Four different type of multi carrier PWM methods are conferred in proposed topology. In all four multi carrier PWM techniques,  $M_A$  is continued at 0.9 and  $M_F$  is at 40. The fundamental component of the inverter output voltage and THD are detected by MATLAB simulation environment. In all four multi carrier PWM method, bipolar multi carter PWM technique is used. In bipolar multi carrier PWM method, "N-1" high frequency carrier waves are used for "N" numeral of voltage levels.

A. In-Phase disposition level shift PWM (IPD-LSPWM) Method

The high frequency multi carter signals, level are shifted in this pulse width modulation method.

One volt of equal amplitude assigned to all high frequency multi carrier waves and a frequency of 2 kHz is assigned to all carrier waves. The level shifted high frequency multi carter signals are associated with fundamental frequency alignment sinusoidal trend which

Satyanarayana, International Journal on Emerging Technologies

10(3): 148-159(2019)

154

is shown in Fig. 6. The dissimilar stages of the output wave is noticed and interpreted to harvest the pulsations which are essential to activate every single switch in the inverter. In directive to acquire three phase inverter structure, the sine trend is phase lifted by 120°.

Fig. 6. Modulating Sine Trend and Triangular Trend for IPD-LSPWM at  $M_A=0.9$  and  $M_F = 40$ .

## B. Anti-phase disposition level-shift PWM (APD - LSPWM) method

Every single high frequency multi carrier signal is 180° phase with adjoining high frequency multi carrier signal. The equal degree of 1 V and rate of recurrence of 2 kHz assigned to all high frequency carrier waves. The high frequency triangular carter signals are associated with the fundamental frequency reference sinusoidal trend which is presented in Fig. 7.

fundamental frequency reference wave. The overlapped multi carrier PWM method is shown in Fig. 8 in directive to harvest the triggering pulses.

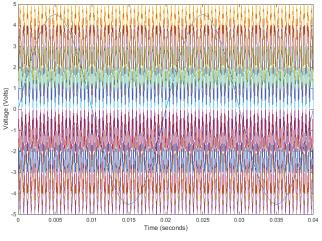

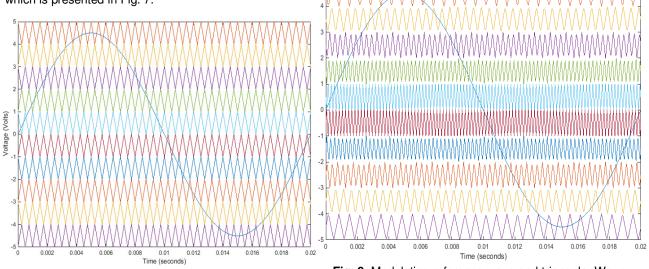

D. Variable frequency PWM (VFPWM) method

In this multi carrier PWM method, equal amplitude of one volt and frequency of 1.5 kHz, 2 kHz, 3 kHz, 4 kHz, 5 kHz are assigned to high frequency carrier waves. Low (1.5 kHz) frequency is assigned to uppermost carrier wave and high frequency (5 kHz) assigned to lower most carrier wave. These high frequency triangular waves are associated with fundamental frequency reference sine wave which is exposed in Fig. 9.

**Fig. 7.** Modulating Sine Trend and Triangular Trend for APD-LSPWM at  $M_A = 0.9$  and  $M_F = 40$ .

### C. Carrier overlap PWM (COPWM) method

In this multi carrier PWM method, equal amplitude of one volt and frequency of 2 kHz assigned to high rate of recurrence carrier waves. The high rate of recurrence carrier wave are overlapped and associated with

### **VI. SIMULATION RESULTS AND DISCUSSIONS**

Dissimilar multi carrier PWM performances are functional to the suggested three phase multilevel module multilevel inverter structure. The significance of  $M_A$  is continued at 0.9 and significance of  $M_F$  is

Satyanarayana, International Journal on Emerging Technologies 10(3): 148-159(2019)

sustained at 40. A proportional study has been carried out the essential value of inverter peak output voltage and THD by Fast Fourier Transform (FFT) analysis. The topology constraints involved in Simulink model:

$$F_c = 2 \ kHz; \ F_m = 50 H_z; \ A_m = 4.5 \ V; \ A_c = 5 V$$

Three phase Star connected resistive load (per phase resistance R = 50  $\Omega$ ).

Inverter phase voltage simulation is exposed in Fig.10. In MATLAB simulation five dc voltage sources are connected to invert input terminal. Each and every dc voltage source allotted to voltage of 46 V. The targeted peak voltage is 230 V.

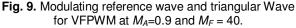

Fig. 10. Simulation of Single Phase 11 Level Inverter Circuit.

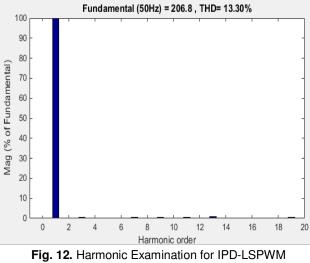

Inverter voltage and it harmonic content by using FFT analysis is carried out for in-phase disposition level shifted multi carrier PWM is shown in Fig. 11 and 12. In IPD-LSPWM, 10 triangular carrier waves with 2 kHz frequency modulated with 50 Hz frequency of sinusoidal reference wave.

Fig. 11. Eleven (11) Level Proposed MLM-MLI Inverter Voltage in IPD-LSPWM Technique.

The generated gate pulses are applied to switching devices of MLM-MLI. From simulation results, 230 V peak voltage and total harmonic distortion (THD) of 13.30 % is observed from FFT analysis in inverter output voltage.

Technique.

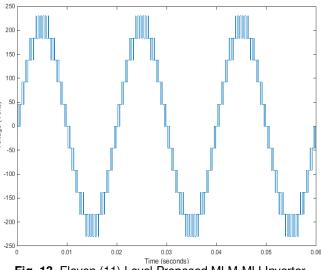

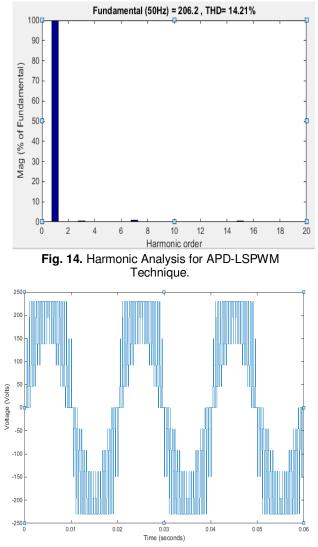

Inverter voltage and it harmonic content by using FFT analysis is carried out for anti-phase disposition level shifted multi carrier PWM is presented in Fig. 13 and 14. In APD-LSPWM, 10 triangular carrier waves with 2 kHz frequency and 180° phase shift of one and other triangular carrier wave modulated with 50 Hz frequency of sinusoidal reference wave. The generated gate pulses are applied to switching devices of MLM-MLI. From simulation results, 230 V peak voltage and total harmonic distortion (THD) of 14.21 % is observed from FFT analysis in inverter output voltage.

Fig. 13. Eleven (11) Level Proposed MLM-MLI Inverter Voltage in APD-LSPWM Technique.

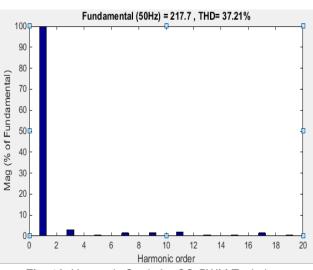

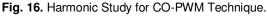

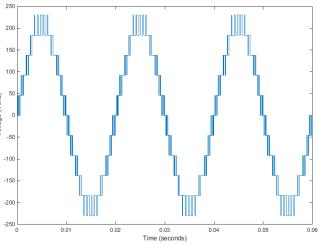

Inverter voltage and it harmonic content by using FFT analysis is carried out for carrier overlap PWM is exemplified in Fig.15 and 16. In CO-PWM, 10 overlapped triangular carrier waves with 2 kHz frequency modulated with 50 Hz frequency of sinusoidal reference wave. The generated gate pulses are applied to switching devices of MLM-MLI. From simulation results, 230 V peak voltage and total harmonic distortion

10(3): 148-159(2019)

(THD) of 37.21 % is observed from FFT analysis in inverter output voltage.

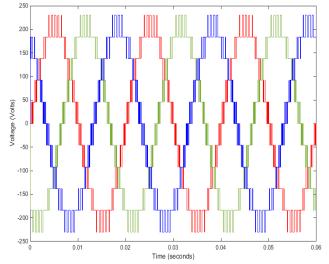

generated by shifting the reference sine wave by 120° and 240°.

Fig. 15. Eleven (11) Level Proposed MLM-MLI Inverter Voltage in CO-PWM Technique.

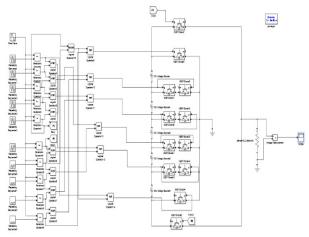

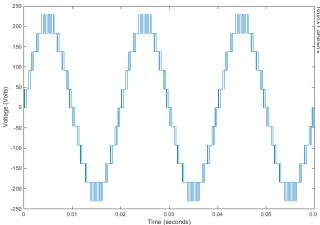

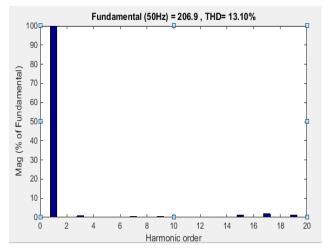

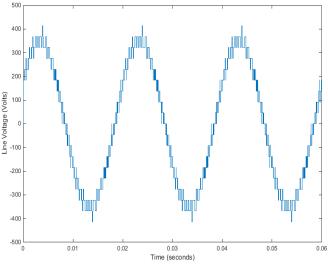

Inverter voltage and it harmonic content by using FFT analysis is carried out for variable frequency PWM is shown in Fig.17 and 18. In VF-PWM, 10 triangular carrier waves with variable frequency of 1.5 kHz, 2 kHz, 3 kHz, 4 kHz and 5 kHz modulated with 50 Hz frequency of sinusoidal reference wave. The generated gate pulses are applied to switching devices of MLM-MLI. From simulation results, 230 V peak voltage and total harmonic distortion (THD) of 13.10 % is observed from FFT analysis in inverter output voltage. Three phase MLM-MLI phase voltages and line voltage are presented in Fig. 19 and 20. In three phase MLM-MLI simulation, variable frequency PWM technique is used. In this control technique, 10 triangular carrier waves with variable frequencies of 1.5 kHz, 2 kHz, 3 kHz, 4 kHz and 5 kHz modulated with 50 Hz frequency of reference sine wave. Generated gate pulses are applied to switching components of inverter circuit for R-phase. Yphase and B-phase inverter circuit gate pulses are

Fig. 17. Eleven (11) Level Proposed MLM-MLI Inverter Output Voltage in VF-PWM Method.

Fig. 18. Harmonic Investigation for VF-PWM Technique.

Satyanarayana, International Journal on Emerging Technologies

10(3): 148-159(2019)

Generated gate pulses are applied to Y-phase and Bphase inverter circuits. From simulation results, 230 V peak voltage and 400 V line voltage are observed for star connected resistive load of 50  $\Omega$  per phase. This three phase inverter circuit is also tested with resistiveinductive (R = 50  $\Omega$  and L = 50 mH) load.

Fig. 19. Proposed MLM-MLI Three Phase Voltage Waveform.

Fig. 20. Line Voltage Waveform for Proposed MLM-MLI Topology.

Table 6: Harmonic Spectrum Comparison for different MCPWM Techniques.

| S.NO. | Peak Value of<br>Inverter Output<br>Voltage(Volts) | Inverter Output Scheme |       |

|-------|----------------------------------------------------|------------------------|-------|

| 1     | 230 V                                              | IPD-<br>LSPWM          | 13.30 |

| 2     | 230 V                                              | APD-<br>LSPWM          | 14.21 |

| 3     | 230 V                                              | CO-PWM                 | 37.21 |

| 4     | 230 V                                              | VF-PWM                 | 13.10 |

The performance analysis of all four PWM methods of proposed MLM-MLI inverter topology for THD and peak value of output voltage is presented in Table 6. From all four methods, VF-pulse width modulation method is given minimum harmonics spectrum in inverter output voltage.

### **VII. CONCLUSION**

In this paper an improved version of multilevel module multilevel inverter topology is presented. The proposed topology reduces switching components, switching losses and gate driver circuitry compared to existing topology. Analytical analysis and optimal structures of proposed topology is analyzed for n-levels. The proposed topology simulation has been carried out for eleven level inverter and it also compared with existing eleven level inverter topology. Output voltage of eleven level inverter topology and its harmonic spectrum have been evaluated with different types of multicarrier PWM techniques. From simulation results, it confirmed that, variable frequency pulse width modulation (VFPWM) offers lowest (13.10%) total harmonic distortion (THD) in eleven level inverter output voltage.

### **VIII. FUTURE SCOPE**

The proposed topology required  $\frac{n-1}{2}$  capacitor for nlevels. These capacitors are unequally charged to input dc voltage. So that, the future work of this topology will be balancing the capacitor voltages for n-levels.

### REFERENCES

[1]. Akagi, H. (2017). Multilevel converters: Fundamental circuits and systems. *Proceedings of the IEEE*, *105*(11): 2048-2065.

[2]. Vahedi, H., Sharifzadeh, M., & Al-Haddad, K. (2018). Modified seven-level pack U-cell inverter for photovoltaic applications. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, *6*(3): 1508-1516.

[3]. Leon, J. I., Vazquez, S., & Franquelo, L. G. (2017). Multilevel converters: Control and modulation techniques for their operation and industrial applications. *Proceedings of the IEEE*, *105*(11): 2066-2081.

[4]. Prabaharan, N., & Palanisamy, K. (2017). A comprehensive review on reduced switch multilevel inverter topologies, modulation techniques and applications. *Renewable and Sustainable Energy Reviews*, *76*: 1248-1282.

[5]. Lee, S. S. (2018). Single-Stage Switched-Capacitor Module (S3CM) Topology for Cascaded Multilevel Inverter. *IEEE Transactions on Power Electronics*, *33*(10): 8204-8207.

[6]. Hosseinzadeh, M. A., Sarbanzadeh, M., Sarbanzadeh, E., Rivera, M., Babaei, E., & Riveros, J. (2017, December). New cascaded multilevel converters based on switched-diode six-level configuration. In *2017 IEEE Southern Power Electronics Conference (SPEC)*: 1-6.

[7]. Boora, K., & Kumar, J. (2017). General topology for asymmetrical multilevel inverter with reduced number of switches. *IET Power Electronics*, *10*(15): 2034-2041.

[8]. Samsami, H., Taheri, A., & Samanbakhsh, R. (2017). New bidirectional multilevel inverter topology with staircase cascading for symmetric and asymmetric structures. *IET Power Electronics*, *10*(11): 1315-1323.

[9]. Ebrahimi, J., Babaei, E., & Gharehpetian, G. B. (2011). A new multilevel converter topology with reduced number of power electronic components. *IEEE Transactions on industrial electronics*, *59*(2): 655-667.

[10]. Gupta, K. K., Ranjan, A., Bhatnagar, P., Sahu, L. K., & Jain, S. (2015). Multilevel inverter topologies with reduced device count: A review. *IEEE transactions on Power Electronics*, *31*(1): 135-151.

[11]. Samadaei, E., Gholamian, S. A., Sheikholeslami, A., &Adabi, J. (2016). An envelope type (E-Type) module: asymmetric multilevel inverters with reduced components. *IEEE Transactions on Industrial Electronics*, *63*(11): 7148-7156.

[12]. Samadaei, E., Sheikholeslami, A., Gholamian, S. A., & Adabi, J. (2017). A square T-type (ST-Type) module for asymmetrical multilevel inverters. *IEEE Transactions on power Electronics*, *33*(2): 987-996.

[13]. Alishah, R. S., Hosseini, S. H., Babaei, E., Sabahi, M., & Zare, A. (2016). Extended high step-up structure for multilevel converter. *IET Power Electronics*, *9*(9): 1894-1902.

[14]. Alishah, R. S., Hosseini, S. H., Babaei, E., & Sabahi, M. (2016). A new general multilevel converter topology based on cascaded connection of submultilevel units with reduced switching components, DC sources, and blocked voltage by switches. *IEEE Transactions on Industrial Electronics*, *63*(11): 7157-7164.

[15]. Siddique, M. D., Mekhilef, S., Shah, N. M., & Memon, M. A. (2019). Optimal design of a new cascaded multilevel inverter topology with reduced switch count. *IEEE Access*, *7*: 24498-24510.

[16]. Jayabalan, M., Jeevarathinam, B., & Sandirasegarane, T. (2017). Reduced switch countpulse width modulated multilevel inverter. *IET Power Electronics*, *10*(1): 10-17.

[17]. Saeedian, M., Adabi, J., & Hosseini, S. M. (2017). Cascaded multilevel inverter based on symmetricasymmetric DC sources with reduced number of components. *IET Power Electronics*, *10*(12): 1468-1478. [18]. Sabyasachi, S., Borghate, V. B., Karasani, R. R., Maddugari, S. K., & Suryawanshi, H. M. (2017). Hybrid control technique-based three-phase cascaded multilevel Inverter topology. *IEEE Access*, *5*: 26912-26921.

[19]. Alishah, R. S., Hosseini, S. H., Babaei, E., & Sabahi, M. (2017). Optimization assessment of a new extended multilevel converter topology. *IEEE Transactions on Industrial Electronics*, *64*(6): 4530-4538.

[20]. Alishah, R. S., Hosseini, S. H., Babaei, E., Sabahi, M., & Gharehkoushan, A. Z. (2016). Optimal design of new cascade multilevel converter topology based on series connection of extended sub-multilevel units. *IET Power Electronics*, *9*(7): 1341-1349.

[21]. Alishah, R. S., Hosseini, S. H., Babaei, E., & Sabahi, M. (2016). Optimal design of new cascaded switch-ladder multilevel inverter structure. *IEEE Transactions on Industrial Electronics*, *64*(3): 2072-2080.

[22]. Siddique, M. D., & Sarwar, A. (2016). Performance analysis of carrier based PWM technique for three level diode clamped multilevel inverter with different reference signals. In *2016 IEEE 7th Power India International Conference (PIICON)*: 1-6.

[23]. Konstantinou, G., Pou, J., Ceballos, S., Darus, R., & Agelidis, V. G. (2015). Switching frequency analysis of staircase-modulated modular multilevel converters and equivalent PWM techniques. *IEEE Transactions on Power Delivery*, *31*(1): 28-36.

[24]. Dahidah, M. S., Konstantinou, G., & Agelidis, V. G. (2014). A review of multilevel selective harmonic elimination PWM: formulations, solving algorithms, implementation and applications. *IEEE Transactions on Power Electronics*, *30*(8): 4091-4106.

[25]. Memon, M. A., Mekhilef, S., & Mubin, M. (2018). Selective harmonic elimination in multilevel inverter using hybrid APSO algorithm. *IET Power Electronics*, *11*(10): 1673-1680.

**How to cite this article:** Satyanarayana, K.V.V. (2019). A Reduced Switch Count Multilevel Module Multilevel Converter Topology. *International Journal on Emerging Technologies*, **10**(3): 148–159.